Caratteristiche Principali

- Supporto per testare 400 MHz, 533 MHz, 667 MHz, 800 MHz, 1066 MHz e livelli di velocità personalizzati dei segnali DDR2

- Il modo più rapido per acquisire fiducia nella tua interfaccia DDR2 misurando un gran numero di cicli e riportando risultati statistici

- Schermata di misurazione del caso peggiore completamente annotata acquisita e visualizzata nel rapporto, comprese etichette di traccia e livelli di tensione pertinenti

- La funzionalità Stop on test/failure consente all'utente di fare una pausa in un particolare test e rivedere la misura sul display dell'oscilloscopio

- Copertura completa dei test per i test come descritto dalle specifiche JEDEC JESD79-2E e JESD208 e dall'addendum alle specifiche JEDEC Intel DDR2 667/800 Rev. 1.1 e dall'addendum alle specifiche JEDEC Intel DDR2 400/533 Rev. 1.0

La soluzione di test Teledyne LeCroy QPHY-DDR2 è il modo migliore per caratterizzare le interfacce di memoria DDR2. In grado di eseguire misurazioni su 400 MHz, 533 MHz, 667 MHz, 800 MHz, 1066 MHz e gradi di velocità personalizzati, QPHY-DDR2 dispone di una suite completa di test di clock, elettrici e di temporizzazione come specificato dalle specifiche JEDEC e dalle specifiche Intel JEDEC Addendum.

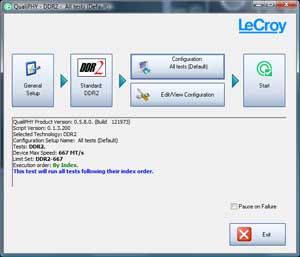

La piattaforma QualiPHY di Teledyne LeCroy fornisce un'interfaccia utente facile da configurare, consente la selezione personalizzata di test e limiti, visualizza i diagrammi di connessione all'utente per garantire una connettività adeguata e genera rapporti con tutti i risultati, inclusi screenshot dei casi peggiori guasti per ogni applicabile test. Inoltre, tutte le forme d'onda testate da QPHY-DDR2 possono essere salvate per condividere facilmente le informazioni o ripetere i test in un secondo momento.

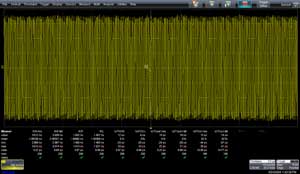

QPHY-DDR2 consente all'utente di ottenere il massimo livello di fiducia nella propria interfaccia DDR2. A causa dell'elevato livello di variabilità nelle misurazioni DDR2, è importante misurare un numero elevato di cicli. Misurando un numero elevato di cicli in un periodo di tempo molto breve, l'utente può essere più sicuro di rilevare i veri punti massimo e minimo per la misurazione.

Oltre alla caratterizzazione automatizzata dei segnali DDR2, QPHY-DDR2 offre anche potenti funzionalità di debug per i segnali DDR2 all'interno dell'oscilloscopio. Le cause principali del guasto possono essere individuate rapidamente e facilmente utilizzando tutti gli strumenti avanzati per i dati seriali all'interno dell'oscilloscopio. Questi includono: SDA II, Eye Doctor™ II, WaveScan™ e molti altri.

Test dell'orologio: questi test eseguono tutti i test dell'orologio come descritto dalla specifica JEDEC appropriata. Questi includono il periodo di clock medio, il periodo di clock assoluto, l'ampiezza media dell'impulso alto/basso, l'ampiezza assoluta dell'impulso alto/basso, il jitter di metà periodo, il jitter del periodo di clock, il jitter del periodo da ciclo a ciclo e l'errore cumulativo su n test di periodo.

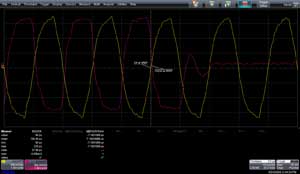

Test elettrici: questi test misurano le caratteristiche elettriche dei segnali DDR2. Mostrato sopra, il test SoutR misura la velocità di variazione dei segnali di dati, strobo e clock. Sono state eseguite oltre 1000 misurazioni della velocità di risposta e l'istanza peggiore è stata visualizzata sullo schermo. I segnali sono annotati con i nomi dei segnali per facilitare l'interpretazione dello schermo. Inoltre, i cursori vengono utilizzati per mostrare all'utente i livelli di tensione tra i quali è stata misurata la velocità di variazione.

Timing Test – Questi test verificano la relazione temporale tra particolari eventi DDR2. Mostrato sopra, il test tDQSCK verifica che il tempo di accesso all'uscita stroboscopica dal segnale di clock rientri nel limite specificato dalla specifica JEDEC appropriata. In questo test, sono state eseguite 5000 misurazioni tDQSCK su tutti i burst di lettura DDR2 e l'istanza peggiore è stata visualizzata sullo schermo.

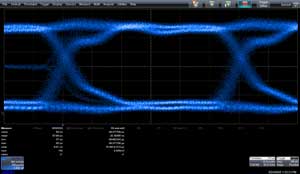

Diagrammi a occhio – I diagrammi a occhio sono un potente strumento per il debug dei segnali di dati seriali. QPHY-DDR2 consente all'utente di creare diagrammi a occhio dei burst di dati di lettura e scrittura per garantire che l'integrità del segnale sia sufficiente in modo tale che i dati vengano campionati correttamente dal ricevitore.

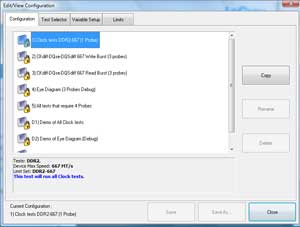

QualiPHY ha molte configurazioni di conformità preimpostate, ma consente anche agli utenti di creare la propria configurazione e set di limiti.

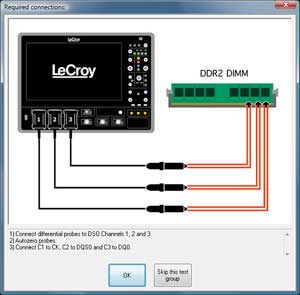

I diagrammi di connessione richiedono all'utente di effettuare le connessioni necessarie.

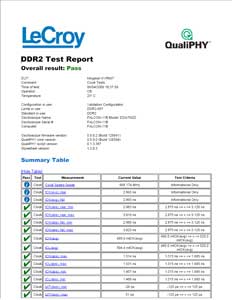

I report di conformità contengono tutti i valori testati, i limiti di test specifici e le schermate. I report di conformità possono essere creati in formato HTML, PDF o XML.

QualiPHY

QualiPHY è progettato per ridurre il tempo, lo sforzo e le conoscenze specialistiche necessarie per eseguire test di conformità su bus seriali ad alta velocità.

- Guida l'utente attraverso ogni configurazione del test

- Esegue ciascuna misurazione in conformità con la relativa procedura di prova

- Confronta ogni valore misurato con i limiti delle specifiche applicabili

- Documenta completamente tutti i risultati

- QualiPHY aiuta l'utente a eseguire i test nel modo giusto, ogni volta!

Specifiche

Test dell'orologio

tCK(avg) – Periodo orologio medio

tCH(avg) – Durata media dell'impulso alto

tCL(avg) – Durata media dell'impulso basso

tCK (abs) – Periodo di clock assoluto

tCH(abs) – Larghezza di impulso alta assoluta

tCL(abs) – Durata assoluta dell'impulso basso

tJIT(dovere) – Jitter di metà periodo

tJIT(per) – Jitter del periodo di clock

tJIT(cc) – Jitter da ciclo a ciclo

tERR(n per) – Errore cumulativo

Debug avanzato

Diagramma a occhio di dati e stroboscopio sul ciclo di lettura

Diagramma a occhio di dati e stroboscopio sul ciclo di scrittura

Test elettrici

SlewR – Immettere la velocità di risposta del fronte di salita

SlewF – Immettere la velocità di risposta del fronte di discesa

VIH(ac) – Logica di ingresso CA alta

VIH(dc) – Ingresso logico CC alto

VIL(ac) – Logica di ingresso CA bassa

VIL(dc) – Ingresso logico CC basso

VSWING – Segnale di ingresso massimo

Oscillazione da picco a picco

SoutR: aumento della velocità di variazione dell'uscita

SoutF – Diminuzione della velocità di variazione dell'uscita

tSLMR – Rapporto di corrispondenza della velocità di variazione dell'uscita

Ampiezza di picco di overshoot CA

Area di superamento CA sopra VDDQ

AC Undershoot Ampiezza di picco

Area di undershoot AC al di sotto di VSSQ

VID(ac) – Tensione di ingresso differenziale CA

VIX(ac) – Tensione del punto di incrocio dell'ingresso differenziale CA

VOX(ac) – Tensione del punto di incrocio dell'uscita differenziale CA

Prove di cronometraggio

tHZ(DQ) – Tempo di alta impedenza DQ da CK/CK#

tLZ(DQ) – Tempo di bassa impedenza DQ da CK/CK#

tLZ(DQS) – Tempo di bassa impedenza DQS da CK/CK#

tHP – CK Larghezza mezzo impulso

tQHS – Fattore di asimmetria mantenimento DQ

tQH – Tempo di mantenimento dell'uscita DQ/DQS da DQS

tDQSH – Larghezza di impulso alta ingresso DQS

tDQSL – Ingresso DQS Larghezza impulso basso

tDSS – Tempo di impostazione del fronte di discesa DQS rispetto al CK

tDSH – Tempo di mantenimento del fronte di discesa DQS da CK

tWPRE – Scrivi il preambolo

tWPST – Scrivi Postambolo

tRPRE – Leggi Preambolo

tRPST – Leggi Postambolo

tDQSQ – Disallineamento tra DQS e DQ

tDQSS – Transizione con blocco DQS al fronte del clock

tDQSCK – Tempo di accesso uscita DQS da CK/CK#

tAC – Tempo di accesso all'uscita DQ da CK/CK#

tDS(base) – Tempo di impostazione ingresso DQ e DM

tDH(base) – Tempo di mantenimento ingresso DQ e DM

tIS(base) – Tempo di impostazione dell'ingresso di controllo e indirizzo

tIH(base) – Tempo di mantenimento dell'ingresso di controllo e indirizzo

tDS1(base) – Tempo di impostazione ingresso DQ e DM (stroboscopio single-ended)

tDH1(base) – Tempo di mantenimento ingresso DQ e DM (stroboscopico single-ended)